IBM a annoncé une nouvelle génération de systèmes de traitement de l'information pour l'intelligence artificielle - Prolum II et IBM Spyre Accelerator. Les deux produits sont conçus pour accélérer l'intelligence artificielle et augmenter les performances des applications institutionnelles. Telum II offre des améliorations significatives avec un cache plus grand et des noyaux à haute performance. Spyre Accelerator termine cela pour fournir des performances encore meilleures pour les applications d'intelligence artificielle.

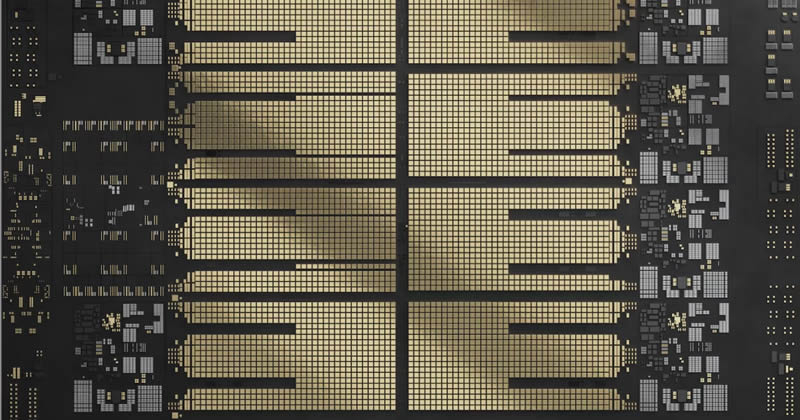

Selon le blog de la société, le nouveau processeur IBM Telum II, développé à l'aide de la technologie nanométrique de Samsung, sera équipé de huit graines de performance élevées fonctionnant à un rythme de 5,5 GHz. Alors que la quantité de cache sur la puce a augmenté de 40%, le cache L3 virtuel a augmenté à 360 Mo et le cache L4 à 2,88 Go. Une autre innovation est l'unité intégrée de traitement des données (DPU) pour les opérations G / O plus rapides et la nouvelle génération de l'intelligence artificielle accélérant.

Telum II offre des améliorations de performances significatives par rapport aux générations précédentes. L'accélérateur d'intelligence artificielle construit atteint 24 milliards de billions de traitement (sommet) par seconde en fournissant quatre fois plus de puissance de traitement. L'architecture d'accélérateur est optimisée pour fonctionner avec des modèles de grande langue et prend en charge un large éventail de modèles d'intelligence artificielle pour une analyse complexe des données texte. De plus, le nouveau processeur prend en charge le type de données INT8 pour augmenter l'efficacité de calcul. Cependant, au niveau du système, Telum II permet une distribution de charge plus efficace en permettant à chaque noyau de processeur d'accéder à l'un des huit accélérateurs d'IA dans un seul module et atteint 192 hauts de performances générales.

IBM a également introduit l'accélérateur de spyre développé conjointement avec IBM Research et IBM Infrastructure Development. Spyre est équipé de 32 noyau d'accélérateur AI, similaire à l'architecture de l'accélérateur intégré dans la puce Telum II. La possibilité de connecter plusieurs accélérateurs d'espionnage au sous-système IBM / O via PCIE augmente considérablement les ressources existantes pour accélérer les charges de travail de l'intelligence artificielle.

Telum II et Spyre sont conçus pour soutenir un large éventail d'exemples d'utilisation de l'intelligence artificielle, y compris l'intelligence artificielle. Cette méthode utilise l'utilisation de plusieurs modèles d'intelligence artificielle en même temps pour améliorer les performances et la précision d'estimation générale. Un exemple de ceci est la détermination de la fraude à l'assurance, dans laquelle les réseaux de neurones traditionnels sont combinés avec succès avec des modèles de langue importants pour augmenter l'efficacité de l'analyse.

Les deux produits ont été introduits lors de la conférence Hot Chips 2024 le 26 août à Palo Alto (Californie, USA). Ils devraient être publiés en 2025.