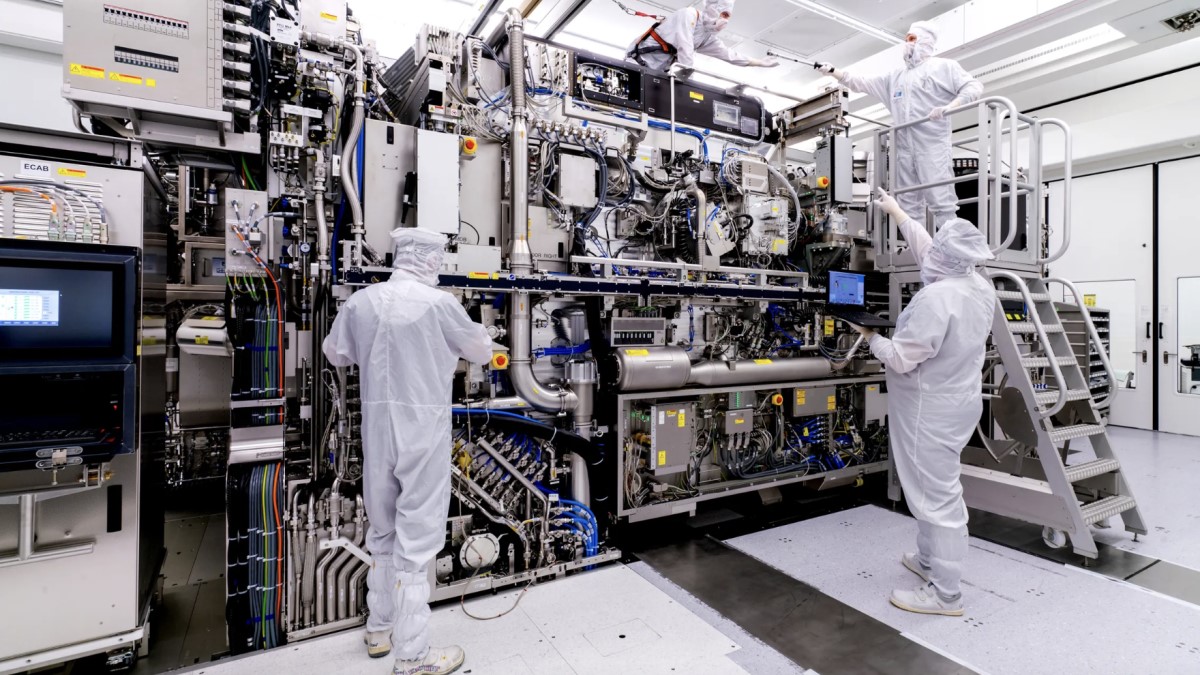

Hollanda merkezli ASML, High-NA EUV litografi aracını kullanarak ilk yarı iletken numunelerin oluşturulduğunu duyurdu. Etkinlik yalnızca ASML için değil aynı zamanda bir bütün olarak High-NA EUV teknolojisi için de önemli bir dönüm noktasıdır.

“Veldhoven’daki High-NA EUV sistemimiz dünyanın ilk 10 nanometre yarı iletkenini bastı. Render işlemi, optikler, sensörler ve aşamalar kaba bir kalibrasyon sürecinden geçtikten sonra yapıldı. Daha sonra sistemi tam performansa getirmeyi ve sahada aynı sonuçları almayı planlıyoruz ” dedi.

Şu anda ASML yalnızca üç Yüksek NA EUV litografi sistemi oluşturmuştur. Biri ASML’nin Veldhoven’deki (Hollanda) genel merkezinde, diğeri ise Intel’in Hillsboro, Oregon yakınlarındaki Amerikan D1X fabrikasında yollandı. Üçüncüsü, Belçika’nın önde gelen yarı iletken araştırma enstitüsü olan Imec’te oluşturulacak.

ASML, tüm yarı iletken endüstrisi için önemli bir kilometre taşı olan High-NA EUV litografi sistemini kullanarak bir numunenin başarılı üretimini duyuran ilk şirket gibi görünüyor. ASML, Twinscan EXE:5000 tarayıcısını yalnızca teknolojinin araştırılması ve geliştirilmesi amacıyla kullanmayı amaçlamaktadır.

Buna karşılık Intel, çiplerin seri üretimi için yüksek sayısal açıklığa sahip EUV litografinin nasıl kullanılacağını öğrenmek için Twinscan EXE:5000’i kullanmayı planlıyor. Tarayıcı, tescilli Intel 18A işlem teknolojisini (1,8 nm sınıfı) kullanan Ar-Ge projeleri için kullanılacaktır. Ancak yeni nesil tarayıcı Twinscan EXE:5200’ün 14A proses teknolojisine (1,4 nm sınıfı) göre çip üretiminde kullanılması planlanıyor.

0,55 sayısal açıklık optikleriyle donatılmış ASML Twinscan EXE:5200 tarayıcı, 13 nm çözünürlük sağlayan mevcut EUV sistemlerine göre önemli bir gelişme olan 8 nm çözünürlükte çip özelliklerini yapmak üzere tasarlanmış. Yeni teknoloji, Low-NA EUV cihazlarıyla karşılaştırıldığında transistör boyutunu 1,7 kat azaltıyor ve transistör yoğunluğunu poz başına 2,9 kat artırıyor.

Düşük NA tarayıcıları da bu düzeyde çözünürlük elde edebilir ancak daha pahalı olan ikili desen yöntemini gerektirir. Seri üretimine 2025-2026 yılında başlanması planlanan 3 nm’nin altındaki standartlara göre çip üretimi için High-NA EUV litografiye sahip sistemlere geçiş yapılması gerekiyor. High-NA EUV litografinin kullanılması, iki şablonla iki geçiş ihtiyacını ortadan kaldırır, böylece üretim süreçlerini optimize eder, potansiyel olarak üretkenliği artırır ve üretim maliyetlerini azaltır. Öte yandan, yüksek NA araçlarının her birinin maliyeti 400 milyon dolara kadar çıkıyor ve daha gelişmiş süreçlere geçişi zorlaştıran dezavantajlara sahip.